Syracuse University SURFACE

**Dissertations - ALL**

SURFACE

December 2016

# Selective Dynamic Analysis of Virtualized Whole-System Guest Environments

Andrew William Henderson Syracuse University

Follow this and additional works at: https://surface.syr.edu/etd

Part of the Engineering Commons

#### **Recommended Citation**

Henderson, Andrew William, "Selective Dynamic Analysis of Virtualized Whole-System Guest Environments" (2016). *Dissertations - ALL*. 580. https://surface.syr.edu/etd/580

This Dissertation is brought to you for free and open access by the SURFACE at SURFACE. It has been accepted for inclusion in Dissertations - ALL by an authorized administrator of SURFACE. For more information, please contact surface@syr.edu.

#### ABSTRACT

Dynamic binary analysis is a prevalent and indispensable technique in program analysis. While several dynamic binary analysis tools and frameworks have been proposed, all suffer from one or more of: prohibitive performance degradation, a semantic gap between the analysis code and the execution under analysis, architecture/OS specificity, being user-mode only, and lacking flexibility and extendability.

This dissertation describes the design of the Dynamic Executable Code Analysis Framework (DECAF), a virtual machine-based, multi-target, whole-system dynamic binary analysis framework. In short, DECAF seeks to address the shortcomings of existing whole-system dynamic analysis tools and extend the state of the art by utilizing a combination of novel techniques to provide rich analysis functionality without crippling amounts of execution overhead. DECAF extends the mature QEMU whole-system emulator, a type-2 hypervisor capable of emulating every instruction that executes within a complete guest system environment.

DECAF provides a novel, hardware event-based method of just-in-time virtual machine introspection (VMI) to address the semantic gap problem. It also implements a novel instruction-level taint tracking engine at bitwise level of granularity, ensuring that taint propagation is sound and highly precise throughout the guest environment. A formal analysis of the taint propagation rules is provided to verify that most instructions introduce neither false positives nor false negatives. DECAF's design also provides a plugin architecture with a simple-to-use, event-driven programming interface that makes it both flexible and extendable for a variety of analysis tasks.

The implementation of DECAF consists of 9550 lines of C++ code and 10270 lines of C code. Its performance is evaluated using CPU2006 SPEC benchmarks, which show an average overhead of 605% for system wide tainting and 12% for VMI. Three platform-neutral DECAF plugins - Instruction Tracer, Keylogger Detector, and API Tracer - are

described and evaluated in this dissertation to demonstrate the ease of use and effectiveness of DECAF in writing cross-platform and system-wide analysis tools.

This dissertation also presents the Virtual Device Fuzzer (VDF), a scalable fuzz testing framework for discovering bugs within the virtual devices implemented as part of QEMU. Such bugs could be used by malicious software executing within a guest under analysis by DECAF, so the discovery, reproduction, and diagnosis of such bugs helps to protect DECAF against attack while improving QEMU and any analysis platforms built upon QEMU. VDF uses selective instrumentation to perform targeted fuzz testing, which explores only the branches of execution belonging to virtual devices under analysis. By leveraging record and replay of memory-mapped I/O activity, VDF quickly cycles virtual devices through an arbitrarily large number of states without requiring a guest OS to be booted or present. Once a test case is discovered that triggers a bug, VDF reduces the test case to the minimum number of reads/writes required to trigger the bug and generates source code suitable for reproducing the bug during debugging and analysis.

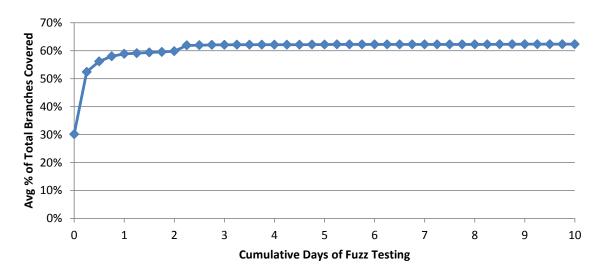

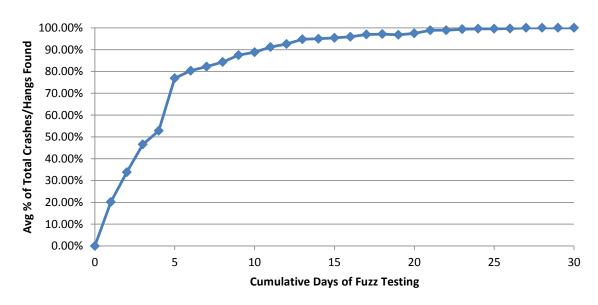

VDF is evaluated by fuzz testing eighteen QEMU virtual devices, generating 1014 crash or hang test cases that reveal bugs in six of the tested devices. Over 80% of the crashes and hangs were discovered within the first day of testing. VDF covered an average of 62.32% of virtual device branches during testing, and the average test case was minimized to a reproduction test case only 18.57% of its original size.

# SELECTIVE DYNAMIC ANALYSIS OF VIRTUALIZED WHOLE-SYSTEM GUEST ENVIRONMENTS

by

Andrew W. Henderson

B.S., Embry-Riddle Aeronautical University, 1999

M.B.A., Jacksonville University, 2004

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering.

Syracuse University

December 2016

Copyright © Andrew W. Henderson 2016

All Rights Reserved

To my wife, Cheryl.

#### ACKNOWLEDGMENTS

The work presented in this thesis could not have been created without the encouragement and guidance provided by many others. I would like to acknowledge those who have helped me throughout this effort.

First and foremost, I am proud to acknowledge my wife Cheryl, daughter Olivia, and father Bill for all of the support and encouragement that they have given me during my doctoral studies. I cannot begin to express how excited I am to spend more time with them after five years of late nights in the lab away from them all. Without their help to make the doctoral process more tenable, I doubt I would have made it through. For this, I will forever be thankful. I look forward to all of the long walks and trips to the park that we will have in our future.

My advisor, Dr. Heng Yin, who has been my mentor in both research and technical pursuits, has shown me the importance of striking a balance between research work and life. His expertise has taught me the importance of communication, attention to detail, and the art of finding "good" research problems to think about. He has also taught me more than I could ever imagine about the fundamentals of research and technical presentation. All of these aspects will serve me very well in the years to come, and I am very grateful that he decided to take a chance on working with the random graduate student that simply walked into his office one day and asked to learn more about his research work. While my advisor has been my primary source of guidance during my time at Syracuse University, he is one of many faculty members that have given me an opportunity to gain both breadth and depth of knowledge during my doctoral studies. Dr. Wenliang Du has provided me with a variety of opportunities to not only explore mobile platform security, but also to lecture in his classes, collaborate with the students in his lab, and discuss research and industry trends and opportunities. Dr. Ehat Ercanli's coursework and guidance introduced me to the world of single board computers, from which has grown so many opportunities for me that I cannot even begin to count them. Dr. Roger Chen has provided valuable mentorship, advice, and insight into teaching students and navigating the world of higher education.

The help and friendship of my labmates and fellow graduate students (both current students and those long since graduated), has made the long doctoral process much more enjoyable. In particular, the guidance of Lok, Aravind, and Mu and the company of Qian, Xunchao, Rundong, Amit, Mahmuda, and Yousra have helped see me through qualifier exams, submission deadlines, and years of cold and snowy Syracuse weather.

Intelligent Automation, which has funded my research for the past three years, has been very supportive of my doctoral studies. Dr. Jason Li and Dr. Julia Deng have both helped to mentor me through the process of creating, writing, and presenting funding proposals and technical reports. Their guidance has also provided me with training that will serve me well as a principle investigator on my own research projects in the future.

## TABLE OF CONTENTS

|    |       |         |                                             | Page |

|----|-------|---------|---------------------------------------------|------|

| A] | BSTR  | ACT .   |                                             | i    |

| LI | ST OI | TABL    | ES                                          | xi   |

| LI | ST OI | FFIGU   | RES                                         | xii  |

| 1  | Intro | duction |                                             | 1    |

|    | 1.1   | Dynan   | nic analysis design goals                   | 2    |

|    | 1.2   | Harder  | ning DECAF against malicious guest activity | 5    |

|    | 1.3   | Overvi  | iew of dissertation                         | 7    |

|    | 1.4   | Previo  | us publications                             | 8    |

| 2  | Back  | ground  |                                             | 9    |

|    | 2.1   | Proces  | s-level dynamic analysis                    | 9    |

|    | 2.2   | Systen  | n-level dynamic analysis                    | 11   |

|    | 2.3   | Using   | fuzzing for dynamic analysis                | 13   |

| 3  | DEC   | AF .    |                                             | 16   |

|    | 3.1   | Key cł  | nallenges                                   | 17   |

|    |       | 3.1.1   | DECAF components                            | 21   |

|    |       | 3.1.2   | Example DECAF Plugin                        | 25   |

|    | 3.2   | Selecti | ive Code Instrumentation                    | 27   |

|    | 3.3   | Just-in | -Time VMI                                   | 32   |

|    |       | 3.3.1   | Goals and Challenges                        | 32   |

|    |       | 3.3.2   | Solution                                    | 33   |

|    | 3.4   | Precise | e Lossless Dynamic Taint Analysis           | 37   |

|    |       | 3.4.1   | Taint Propagation in CPU Registers          | 38   |

|    |       | 3.4.2   | Taint Propagation in Memory and IO Devices  | 41   |

|    |       | 3.4.3   | Asynchronous Tainting                       | 42   |

## Page

|   | 3.5   | Forma     | Il Model and Definitions                             | 44  |

|---|-------|-----------|------------------------------------------------------|-----|

|   |       | 3.5.1     | Taint Propagation Rules in Practice                  | 46  |

|   |       | 3.5.2     | Verifying Taint Propagation Rules                    | 48  |

|   |       | 3.5.3     | Constructing Tainting Rules                          | 51  |

|   | 3.6   | Evalua    | ation                                                | 61  |

|   |       | 3.6.1     | SPEC CPU2006 Benchmarks                              | 62  |

|   |       | 3.6.2     | Per-Trace Verification of DECAF's Tainting           | 65  |

|   |       | 3.6.3     | API Tracer                                           | 69  |

|   |       | 3.6.4     | Keylogger Detector                                   | 71  |

|   |       | 3.6.5     | Instruction Tracer                                   | 74  |

|   | 3.7   | Limita    | ations of DECAF                                      | 77  |

| 4 | Virtu | ual Devi  | ce Fuzz Testing                                      | 80  |

|   | 4.1   | VDF (     | Overview                                             | 82  |

|   | 4.2   | Backg     | round                                                | 84  |

|   |       | 4.2.1     | Understanding guest access of virtual devices        | 87  |

|   |       | 4.2.2     | Understanding memory mapped I/O                      | 88  |

|   | 4.3   | Fuzzir    | ng virtual devices                                   | 91  |

|   |       | 4.3.1     | Fuzzing workflow                                     | 93  |

|   |       | 4.3.2     | Virtual device record and replay                     | 96  |

|   |       | 4.3.3     | Selective branch instrumentation                     | 104 |

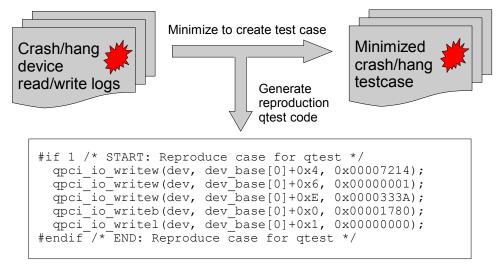

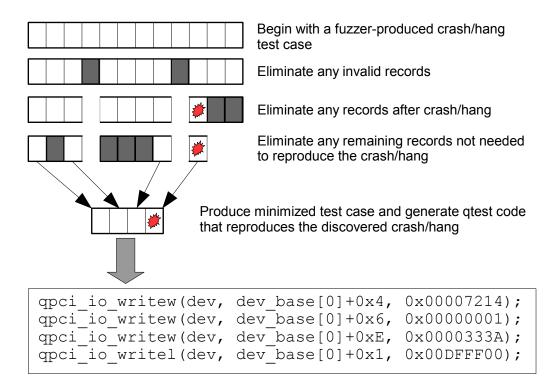

|   |       | 4.3.4     | Creation of minimal test cases                       | 107 |

|   | 4.4   | Evalua    | ation                                                | 109 |

|   |       | 4.4.1     | Virtual device coverage and bug discovery            | 110 |

|   |       | 4.4.2     | Classification of all discovered virtual device bugs | 113 |

|   | 4.5   | Limita    | ations of VDF                                        | 121 |

|   | 4.6   | Relate    | d Work                                               | 122 |

| 5 | Sum   | mary .    |                                                      | 126 |

| А | Rule  | e constru | action and verification: A 2-bit and example         | 128 |

| В | VDF   | F Sample  | e Fuzzing Results: SDHCI Virtual Device              | 133 |

|                    | Page |

|--------------------|------|

| LIST OF REFERENCES | 137  |

| VITA               | 145  |

## LIST OF TABLES

| Table | e                                                                                                                                                                                                                                                                                                                                                       | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | The scope and purpose of existing dynamic analysis tools.                                                                                                                                                                                                                                                                                               | 14   |

| 3.1   | DECAF supported x86 instructions.<br>The tainting rules for all these instructions are sound, and most are also precise. The imprecise ones are marked with "*".                                                                                                                                                                                        | 40   |

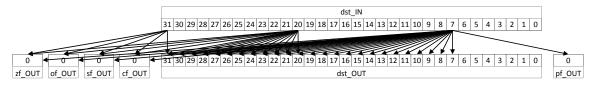

| 3.2   | Flow Type Results for x86 Instructions Flow Types: (U)p, (D)own, (I)n-place, (A)ll-around, (S)pecial, (N)ot-Supported, (S)pecial, (E)ax is tainted in cmpxchg, * - Zeroing Idiom, <b>Boldface</b> - Generated Policy is more precise                                                                                                                    | 55   |

| 3.3   | Precise Rules and Verification Results: Length of operands verified (in bits). $\checkmark$ Verified for all lengths. * Shift amount is untainted. <sup>z</sup> Non-zero operand for bsf, bsr.                                                                                                                                                          | 59   |

| 3.4   | New Precise Bit-level Taint Rules: rcr and bsr are similar to rcl and bsf respectively, and so omitted. The bsf rule is shown for a 16-bit value which must be non-zero, and the rule for rcl is precise only when the rotate amount is untainted. x1, x2, and cf (carry flag) are the operands while t1, t2, and tcf are the respective shadow taints. | 60   |

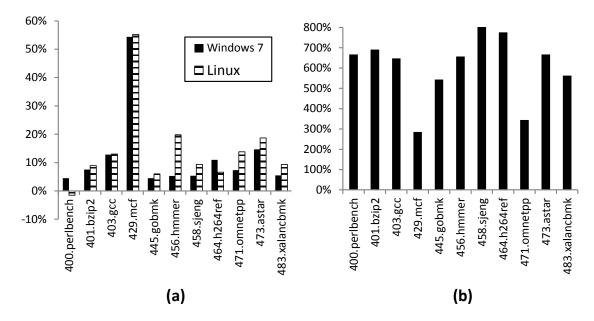

| 3.5   | Execution Overhead for DECAF and DECAF with VMI on different architec-<br>ture/OSs without tainting.                                                                                                                                                                                                                                                    | 63   |

| 3.6   | Code breakdown of DECAF, VMI, and various plugins. The code introduced by DECAF in addition to the code of QEMU, which by itself has over 500K LOC.                                                                                                                                                                                                     | 64   |

| 3.7   | Trojan.Win32.KeyLogger Trace.                                                                                                                                                                                                                                                                                                                           | 72   |

| 3.8   | Comparing DECAF with TEMU on tainted shell commands.<br>"n / m" indicates that "n" bytes are tainted, and "m" tainted EIPs are observed                                                                                                                                                                                                                 | 73   |

| 4.1   | QEMU virtual devices seed data sources.                                                                                                                                                                                                                                                                                                                 | 97   |

| 4.2   | QEMU virtual devices tested with VDF                                                                                                                                                                                                                                                                                                                    | 110  |

| A.1   | Query Results for 2-bit and                                                                                                                                                                                                                                                                                                                             | 130  |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                          | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1  | The overview of DECAF.                                                                                                                                                                                                                                                                                      | 23   |

| 3.2  | A sample plugin for tracking tainted keystrokes.                                                                                                                                                                                                                                                            | 24   |

| 3.3  | DECAF inserts instruction execution callbacks into the original TCG code stream (a) to create an instrumented opcode stream (b) to trigger helper function calls to plugin callback functions.                                                                                                              | 29   |

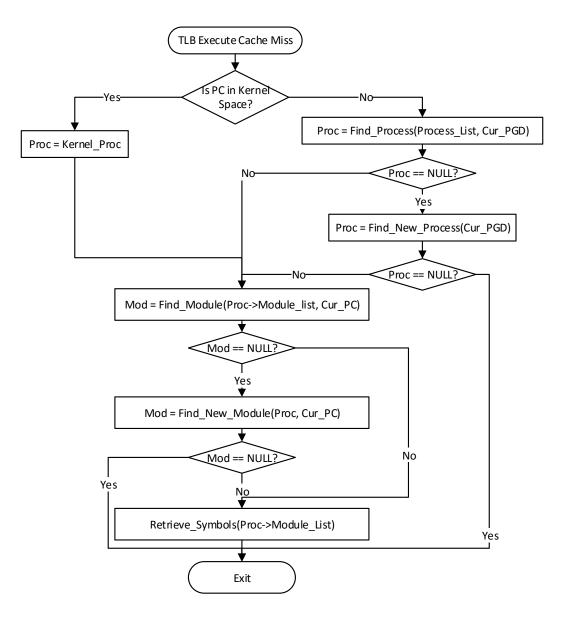

| 3.4  | The VMI flowchart                                                                                                                                                                                                                                                                                           | 34   |

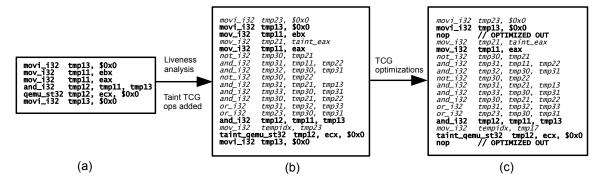

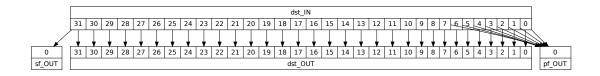

| 3.5  | Register liveness tests determine which TCG instructions in the TB (a) should<br>be instrumented for taint propagation, and instrumentation is inserted as needed<br>(b). TCG's optimization logic eliminates unnecessary opcodes, resulting in an<br>optimized, instrumented TB (c).                       | 39   |

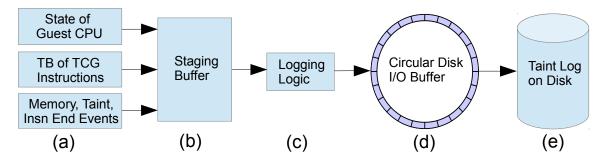

| 3.6  | All events(a) are logged into a staging buffer(b). Logging logic(c) decides which events should be recorded and places them into a circular buffer(d) that is asynchronously written to disk(e)                                                                                                             | 43   |

| 3.7  | Example SMT queries checking for information flow (equation 3.1) from the low bit a of an input to the 4th bit b of an operation output. The first query, for not, is unsatisfiable, indicating no flow. The second query, for add, is satisfiable, for instance by $x1 = 0$ and $x2 = 0xf$ : there is flow | 56   |

| 3.8  | Information flow of dst in or instruction                                                                                                                                                                                                                                                                   | 56   |

| 3.9  | Information flow of bits 7, 20 and 31 of dst in sbb instruction                                                                                                                                                                                                                                             | 57   |

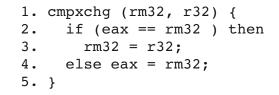

| 3.10 | Pseudocode for cmpxchg (flags are omitted)                                                                                                                                                                                                                                                                  | 58   |

| 3.11 | CINT2006 benchmarks that measure overhead for VMI (a) and inline taint propagation (b).                                                                                                                                                                                                                     | 64   |

| 3.12 | Per-Trace Verification Overview                                                                                                                                                                                                                                                                             | 66   |

| 3.13 | Trace entry for and bug                                                                                                                                                                                                                                                                                     | 68   |

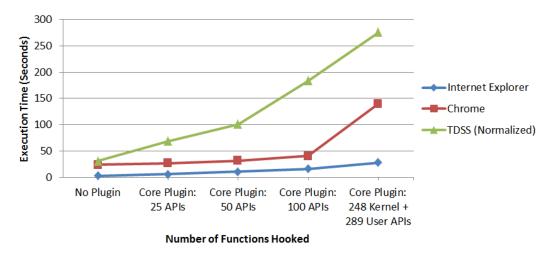

| 3.14 | Evaluation of API Tracer plugin.                                                                                                                                                                                                                                                                            | 70   |

| 3.15 | A simple buffer overflow example                                                                                                                                                                                                                                                                            | 75   |

| 3.16 | Buffer overflow detection on ARM.                                                                                                                                                                                                                                                                           | 75   |

## Figure

| Figu        | re                                                                                                                                                                                                    | Page |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.17        | Buffer overflow detection on x86.                                                                                                                                                                     | 76   |

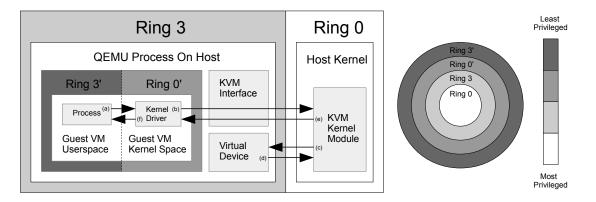

| 4.1         | Device access request originating from inside of a QEMU/KVM guest. Note that the highest level of privilege in the guest (ring 0') is still lower than that of the QEMU process on the host (ring 3). | 87   |

| 4.2         | The x86 address space layout for port- and memory-mapped I/O                                                                                                                                          | 90   |

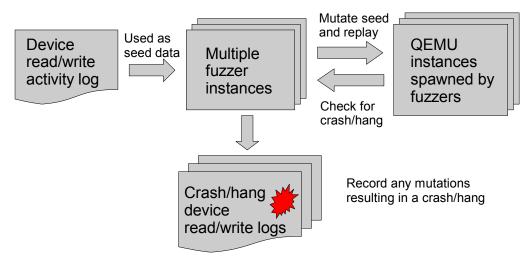

| 4.3         | VDF's process for performing fuzz testing of QEMU virtual devices                                                                                                                                     | 94   |

| 4.4         | The record format of VDF for an MMIO read/write event.                                                                                                                                                | 98   |

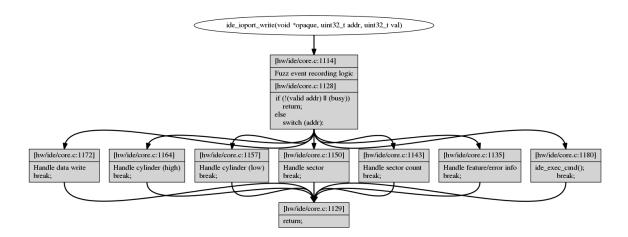

| 4.5         | Simplified control flow graph of the ide_ioport_write() function within the QEMU IDE core.                                                                                                            | 100  |

| 4.6         | Sample branch coverage data for the <code>voice_set_active()</code> function within the AC97 virtual device.                                                                                          | 106  |

| 4.7         | Process for minimizing test cases.                                                                                                                                                                    | 107  |

| 4.8         | Average percentage of branches covered during fuzz testing.                                                                                                                                           | 111  |

| 4.9         | Average percentage of total bugs discovered during fuzz testing                                                                                                                                       | 112  |

| 4.10        | The backtrace of the deadlock in the worker thread pool shutdown, which occurs in the TPM backend (entries #2 and #3 in the backtrace).                                                               | 119  |

| A.1         | SMT2 for 2-bit and                                                                                                                                                                                    | 129  |

| A.2         | SMT2 for verifying the 2-bit and rule                                                                                                                                                                 | 131  |

| A.3         | Sat model for simple 2-bit and rule                                                                                                                                                                   | 132  |

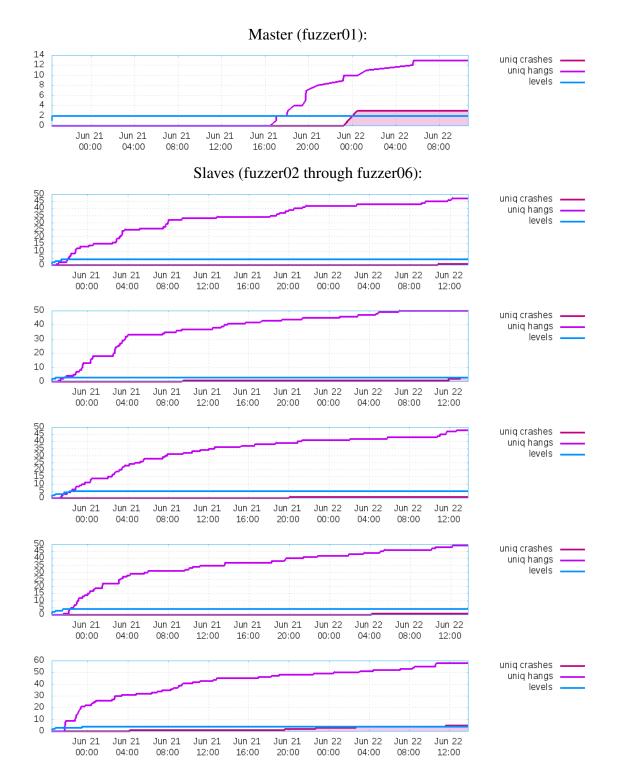

| <b>B</b> .1 | Function call depth and test cases triggering crashes and hangs during the fuzzing of the SDHCI virtual device in QEMU source file hw/sd/sdhci.c.                                                     | 135  |

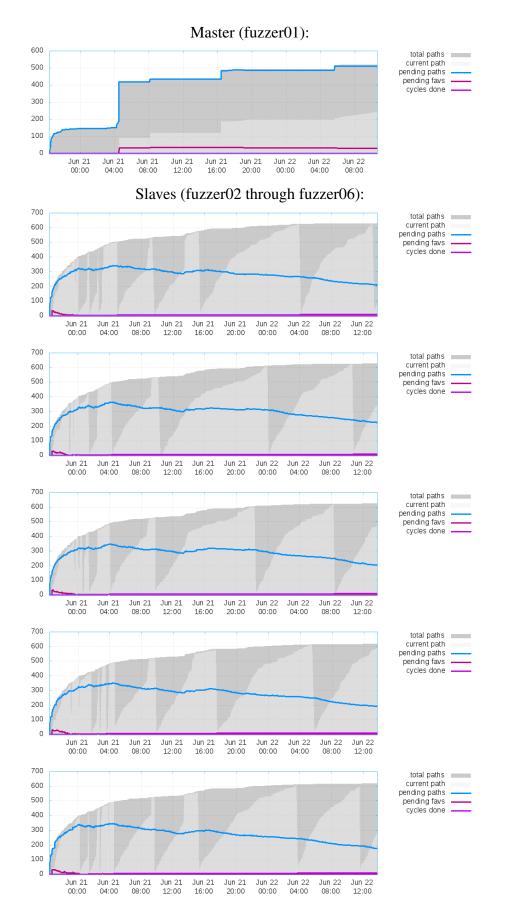

| B.2         | Discovered, explored, and pending paths during the fuzzing of the SDHCI vir-<br>tual device in QEMU source file hw/sd/sdhci.c.                                                                        | 136  |

## **1. INTRODUCTION**

Dynamic analysis is the observation and modification of a guest system as it executes for the purpose of understanding the runtime behavior of that system. It has demonstrated its strength in many research problems, such as malware analysis, protocol reverse engineering, vulnerability signature generation, software testing, profiling, and performance optimization. While static analysis, the examination of code or binaries without requiring the execution of that code, can determine many aspects of individual binaries (control flow graphs, path predicates, use of uninitialized memory, "dead code" that can never be reached, etc.), it is unable to determine behaviors that are only observable at runtime. Examples of such runtime behaviors are interactions among concurrent threads, dynamically modified/created code, time-sensitive logic, and complex multi-process interactions via IPC.

Compared to process-level binary instrumentation and analysis, whole-system dynamic binary analysis has unique advantages. First, it provides a complete view of the guest system, including the OS kernel and all running applications, which enables the analysis of kernel activity and the interactions among multiple user-space processes. Second, the code instrumentation and analysis are performed from entirely outside of the context of the guest system under analysis (typically by executing the guest within a virtual machine (VM)). In contrast, process-level instrumentation tools share the same memory space as the instrumented program execution. Leveraging virtualization techniques, whole-system dynamic binary analysis provides better transparency and stronger isolation than that of process-level instrumentation tools. This is especially important within the context of analyzing malicious code that attempts to detect, evade, and/or tamper with the analysis environment. To discover vulnerabilities within the infrastructure of modern software frameworks, be they embedded, virtualized, or desktop, we must be able to capture and analyze the complete execution of some functionality of interest within an arbitrarily complex guest environment.

#### 1.1 Dynamic analysis design goals

A generic, whole-system dynamic binary analysis platform that can instrument any portion of the guest's execution environment is highly desirable, but challenging to design and create. Unless system-wide dynamic analysis is performed at a reasonable speed, it is useless. Observation of time-sensitive runtime events, such as network communications or GUI interactions, is one of the primary reasons to use dynamic analysis over static analysis methods. Time-sensitive events must be performed in a timely fashion within an instrumented guest to be useful and representative of their non-instrumented execution.

The two primary limitations of dynamic analysis are that guest code must be executed to be observed and that overhead is imposed by the instrumentation necessary to observe, and optionally record, the behavior of the guest. The analysis of every executed instruction within the guest is infeasible. The performance and storage overhead of such a task is too great, and the analysis of such a large dataset is not possible within a reasonable timeframe. In addition, any instrumentation added to the system to observe code execution may limit or interfere with the functionality of the code under observation.

Some subset of the guest's entire execution, such as the behavior of a particular user-space process or kernel module, is typically the desired subject of an analysis. However, the interaction of this subset with the remainder of the guest environment context must be considered. Because of this, it is infeasible to extract only the guest code of interest and observe its execution in isolation. **Therefore, this dissertation makes the thesis statement that it is possible to unobtrusively dynamically analyze a subset of the guest system's execution while that subset executes within the context of the guest. In particular, the following questions must all be satisfactorily answered to prove this thesis statement to be true:**

- 1. How and when is context information about the guest environment gathered? Specifically, virtual machine instrospection (VMI) [58] must be implemented in a way that effectively gathers all required guest context information at the proper time to accurately reconstruct the semantics of the guest environment. Existing VMI approaches place an agent within the guest to gather guest context information [82], or continually poll the guest environment [66] (which incurs additional overhead to guest execution). Is there a better way to accomplish this semantic reconstruction without adding unreasonable instrumentation overhead?

- 2. How can you specify which subset of code within the guest to analyze? Specifically, how is it determined what user or kernel space addresses belong to code of interest? How are these pages of virtual memory mapped to physical memory locations?

How are only those code sections selectively instrumented, rather than instrumenting all code within the guest?

- 3. How is selective instrumentation of the guest performed without modifying guest execution? Specifically, the overhead for guest execution speed overhead must be low enough that guest behavior is unchanged, and no additional instrumentation (such as a VMI agent) must execute within the context of the guest. The order of instructions executed within the guest must not be perturbed, and any instrumentation added to the guest to collect information must not have side effects that impact guest execution.

- 4. How can these principles of selective dynamic analysis be coupled with existing analysis tools to form a complex, focused analysis effort? How can heavyweight analysis tools be selective applied to accomplish analysis efforts that were previously considered infeasible?

This dissertation addresses these four questions by presenting a novel new whole-system dynamic analysis platform capable of selectively applying heavy-weight instrumentation to any subset of code executing within the guest environment. This platform is the Dynamic Executable Code Analysis Framework, or DECAF [62, 63].

Although much research has been performed to make use of whole-system dynamic binary analysis to solve various security problems [40, 41, 46, 77, 90, 91], little attention has been paid to the analysis framework itself. Such tools are often tailored to solve specific problems in an ad-hoc manner. Many times, analysts must still develop new analysis tools from scratch to meet their own specific needs. DECAF is built upon the QEMU whole-system emulator [29], a popular type-2 hypervisor. It aims to address these issues to "Make It Work, Make It Right, Make It Fast". This means that DECAF must not only provide the same set of capabilities as existing analysis systems such as TEMU [82], but it must also follow proper principles in its design. DECAF offers analysis results of better quality, and with a higher correctness guarantee, than TEMU while still conducting analyses more efficiently.

#### 1.2 Hardening DECAF against malicious guest activity

The primary intended purpose of DECAF is the transparent observiton and analysis of the behaviors of malicious software (malware). DECAF is an open-source project [10], and since its first release in January 2013, it has received over 5000 downloads and has been utilized in a number of malware and security analysis studies [25, 37, 54, 85]. It is reasonable to assume that malware authors familiar with DECAF will attempt to attack or evade analysis by attacking and exploiting vulnerabilities in QEMU. *Under no circumstances should activity originating from within the guest be able to attack and compromise QEMU (and by extension, DECAF), so effectively identifying vulnerabilities in QEMU is a difficult, but valuable, problem to consider.*

QEMU uses a virtualized device model: the hardware devices provided to the guest environment are implemented in software within QEMU. Whether QEMU completely emulates the guest CPU or uses another hypervisor, such as KVM [11] or Xen [27], to execute guest CPU instructions, the hardware devices made available to the guest environment will still be QEMU's virtualized devices. Such virtual devices appear as real hardware devices to the guest environment, and can be interacted with in the same manner. Each virtual device emulates the corresponding interfaces (memory-mapped I/O (MMIO), interrupts, and DMA) of its analogous physical device. Virtual devices may completely emulate the internal state of a piece of hardware, provide a pass-through to a physical device on the host system, or provide some combination of the two.

Because these virtual devices are part of the QEMU binary, they execute at a higher level of privilege than any code executing within the guest environment. They are not directly part of the guest environment, per se, but they are QEMU subsystems that the guest environment directly interacts with. Because of this, a malicious or misbehaving guest may attempt to use these virtual devices in an unpredictable manner. QEMU's virtual devices are a common source of security vulnerabilities [4, 5, 6, 7], are written by a number of different authors, and the most complex virtual devices are implemented using thousands of lines of code. Therefore, it is desirable to discover an effective and efficient method to test these devices in a scalable and automated fashion without requiring expert knowledge of each virtual device's state machine and other internal details.

To ameoliorate the threat of malicious guests attacking DECAF via virtual device bugs, this dissertation also presents Virtual Device Fuzzer (VDF), a novel new fuzz testing [73] framework that provides targeted fuzz testing of QEMU's virtual devices. VDF selectively explores interesting branches within complex programs, namely the portions of the QEMU codebase that implements specific virtual devices. While QEMU does provide a mechanism for testing virtual devices [19], this mechanism is intended for regression testing, rather than the discovery of unknown bugs. By providing such focused testing capable of discovering new bugs within QEMU, VDF aims to better protect not only DECAF against virtual device attacks, but also QEMU in general and any other QEMU-based analysis platforms [40, 50, 82].

Providing proper seed test cases to the fuzzer is important for effective exploring the branches of a program [38, 79], as a good starting seed will focus the fuzzer's efforts in areas of interest within the program. Therefore, VDF utilizes *record and replay* of virtual device activity to create fuzzing seed test cases that are guaranteed to reach states of interest and initialize each virtual device to a known good state from which to start testing. It then mutates this seed data to generate and replay fuzzed inputs that exercise additional branches of interest within the virtual device.

#### 1.3 Overview of dissertation

This dissertation describes the theory and design of DECAF, as well as three of its analysis plugins, and evaluates their ability to provide a whole-system binary analysis solution that provides answers to the four questions laid out by the thesis statement. It also describes the theory and design of VDF and evaluates its ability to test virtual devices, discover any vulnerabilities within the virtual device code, and produce minimized test cases suitable for the reproduction of discovered issues.

The dissertation is presented in the following manner. Chapter 1 is the introduction of the thesis and an overview of the material presented within the dissertation. Chapter 2 is a survey of background material that presents the current state of the art of dynamic analysis at both the whole-system and process levels. Chapter 3 presents the DECAF system, explains the novel contributions of its design, and evaluates both its benchmarked performance and capability to perform common analysis tasks. Chapter 4 presents the VDF system, provides additional background material on QEMU's virtual devices, evaluates VDF by fuzz testing a variety of virtual devices, and analyzes the nature of each discovered virtual device issue. Chapter 5 provides a summary of all findings and conclusions. Finally, Appendix A provides a rule construction and verification example of the dataflow rules used within DECAF's system-wide data flow tracking implementation. Appendix B provides a sample set of coverage and result graphs for the fuzz testing of a virtual device using VDF.

#### **1.4 Previous publications**

The research material presented within this dissertation is derived from three publications. A portion of the DECAF material presented within Chapter 3 was first published as a peer-reviewed conference paper in the Proceedings of the 2014 International Symposium on Software Testing and Analysis (ISSTA '14)[63]. The remainder of the DECAF work presented in Chapter 3 and Appendix A has been peer-reviewed and accepted for publication in a future issue of the IEEE Transactions in Software Engineering[62] journal. The VDF material presented in Chapter 4 is currently under submission as a peer-reviewed conference paper for the 2017 Network and Distributed System Security Symposium (NDSS '17).

## 2. BACKGROUND

This chapter presents a survey of existing dynamic analysis tools and techniques. Understang the capabilities and limitations of these prior works provides an understanding of how the state of the art in whole-system dynamic analysis is advanced by the design and features of the DECAF and VDF systems.

#### 2.1 Process-level dynamic analysis

There are many analysis platforms for process-level binary instrumentation, as the dynamic analysis of user-space processes has been a long-studied technique. Several instrumentation solutions perform data flow analyses (known as "dynamic taint analysis" or "tainting") within the scope of a single process or binary. Such solutions are generally much faster than their counterparts implemented for whole-system analysis because process-level instrumentation is limited in scope to only the instructions executed by a single process, rather than all instructions executed across an entire system.

The Pin [70] API is a flexible C/C++ interface used to create process-level instrumentation tools (known as Pintools). Examples of such Pintools are libdft [69] and Dytan [43]. Pintools do not have the benefit of a plugin development API that works at a semantic level higher than that of individual instructions. Dytan is designed as a platform for prototyping different tainting policies. libdft offers a less flexible, but faster, solution

for tracking explicit data flows. It has the same limitations of other Pintools and only supports instrumenting x86 binaries.

DynamoRIO [32] is a runtime code manipulation system that translates process execution on-the-fly to add, remove, and execute instrumentation. Like Pin, it also supports an instrumentation development API to support instrumentation that is triggered during key events such as the execution of individual instructions, loading of libraries, execution of specific function calls, and triggering of system calls. Example tools created using DynamoRIO trace library function calls, count executed instructions and basic blocks [24], track code coverage during execution, and assist in debugging memory. It supports instrumenting 32/64-bit x86 binaries and 32-bit ARM binaries. Similar in functionality to DynamoRIO is Strata [80], which is another runtime code manipulation system. Strata targets Sparc, MIPS, and x86, but provides a coarser level of instrumentation (system call level) than DynamoRIO.

Many efforts have been made to reduce the runtime overhead of process-level dynamic taint analysis. LIFT [78] assumes that taint propagation is not needed for most code execution, so it optimizes performance by taking the fast paths (without taint instrumentation) most of time. It also exploits extra registers in x86 64-bit architectures to shadow taints in x86 32-bit applications. This is a form of selective instrumentation, though the code is actually duplicated into instrumented and non-instrumented forms and the particular version run for any path through the code is selected dynamically at runtime. Minemu [31] leverages the x86 SSE registers to provide lightweight taint tracking for 32-bit x86 applications. Jee et al [65] build upon libdft to create a system that performs a static analysis on a process to selectively instrument the process for dynamic analysis per

the rules of a Taint Flow Algebra. All of these tainting implementations only track taint status, and apply imprecise and sometimes unsound tainting rules, to achieve high efficiency.

Unlike approaches that sacrifice precision and correctness for performance, Memcheck [81] focuses on applying precise and correct tainting rules to troubleshoot memory errors within a process. It uses bitwise tainting to accurately track which bits of memory within the process's memory space have been initialized. Memcheck is able to detect double freeing of memory, usage of uninitialized variables, overlapping source/destination blocks when copying memory, and memory leaks. It favors correctness over efficiency, and does so without relying upon architecture-specific features (e.g., SSE) to improve runtime performance. The dramatic overhead of Memcheck (an average slowdown of 2650%) makes it unsuitable for analyzing software that performs time-dependent tasks. It supports a number of 32/64-bit architectures, include x86, ARM, MIPS, and PPC.

#### 2.2 System-level dynamic analysis

Whole-system instrumentation platforms leverage binary emulation and VMI, and they have long suffered from poor performance. Typically, the guest environment is executed under some form of virtual machine manager (VMM), such as QEMU [29], VMWare [17], or KVM [11], and the guest is unaware that its execution is being virtualized or emulated. The VMM is augmented to perform some form of instrumentation of the guest environment during the guest's execution. Early whole-system analysis platforms, such as TaintBochs [41], favored accuracy over performance. Ether [48] attempts to elude and analyze VM-aware malware by leveraging Intel VT hardware virtualization extensions. By triggering a debug exception after every instruction, Ether is able to stealthily analyze the state of the system at the cost of heavy execution overhead. However, performing practical, accurate analyses of interactive systems makes the reduction of such high overhead an important focus. ReVirt [51] uses an instrumented UMLinux VMM for the record and replay of compromised guest systems. This allows for more heavyweight analyses based upon repeated replays of previously recorded guest sessions. Aftersight [42] attempts to record information from the guest environment and then analyze it on a different system, offloading the analysis overhead to a different machine.

More recent whole-system instrumentation platforms have been built upon QEMU [29]. Argos [77] performs whole-system taint tracking within honeypot systems for the purpose of generating signatures for network-based attacks. Argos extends the earlier process-level taint tracking system TaintCheck [75]. TEMU [16], part of the BitBlaze binary analysis suite [82], serves as the base for a variety of security analysis tools that perform whole-system analysis, such as HookFinder [91], Panorama [90], and Renovo [67]. TEMU is also not capable of emulating newer OSes such as Windows 7 and 8, and it is only capable of instrumenting x86 platforms. Its design, while feature-rich, creates execution overheads that may be far too heavyweight for simpler analyses that do not require all of TEMU's features.

S2E [40] uses QEMU to perform inline symbolic execution on subsets of guest execution. Guest instructions are transformed into a Low-Level Virtual Machine (LLVM [22]) intermediary representation, and when execution of the guest environment reaches a branch within code of interest, S2E forks the current QEMU process to explore both branches using LLVM-based symbolic execution. While powerful, this process is quite slow and memory intensive. PANDA [50] leverages the LLVM work performed by S2E to create an analysis platform using record and replay. Tasks of interest are executed within the guest platform and recorded in a log, and then the recorded activity is replayed through a PANDA analysis plugin. This allows for increasingly heavyweight analyses to be performed on the same recorded activity without placing heavyweight runtime performance penalties on the guest at recording time.

The DECAF tool is designed to assist in performing such heavyweight analyses by using lightweight plugins to capture detailed system information and instruction traces that provide enough detail to allow other tools to perform heavyweight analyses offline, if necessary. DroidScope [88] is a dynamic analysis platform for the security analysis of the Android OS. The core idea of DroidScope is to seamlessly reconstruct both Dalvik VM-level and OS-level semantic views and to provide a unified interface for Android malware analysis. DroidScope is an extension to DECAF for Android-specific analyses. Table 2.1 summarizes the scope and purpose of existing dynamic analysis tools, including DECAF.

#### 2.3 Using fuzzing for dynamic analysis

Fuzzing [73] can be leveraged for both system- and process-level dynamic analysis. Because dynamic analysis is only useful if the behavior to be observed is triggered during

| ANDROID<br>GUEST             |                 |            | 7              | 7               | 2              |            |            |                 |               |             |           | 7             |             | 7             |                 |          |                 |               |               |             |                 |                 | 7               |           |

|------------------------------|-----------------|------------|----------------|-----------------|----------------|------------|------------|-----------------|---------------|-------------|-----------|---------------|-------------|---------------|-----------------|----------|-----------------|---------------|---------------|-------------|-----------------|-----------------|-----------------|-----------|

| WIN32<br>GUEST               | 2               | >          | 2              |                 | >              | >          | 2          | 2               |               |             | 2         | >             |             | 2             | 2               | 2        | 2               |               | 2             | 2           | 7               | 7               |                 | 7         |

| <b>LINUX</b><br><b>GUEST</b> | >               | 7          | 7              |                 | 7              | 7          |            | 7               | 7             | 7           |           | 7             | 7           | 7             | 7               | 7        | 7               | 7             | 7             | 7           | 7               | 7               |                 | 7         |

| <b>BASED</b><br>UPON         | VMWare          | TaintCheck | QEMU           | DECAF           | N/A            | Pin        | Xen        | TEMU            | LLVM          | Pin         | StarDBT   | Valgrind      | N/A         | QEMU          | TEMU            | N/A      | TEMU            | UMLinux       | QEMU          | N/A         | Bochs           | Valgrind        | Android OS      | QEMU      |

| ARM                          |                 |            | 7              | 7               | 7              |            |            |                 |               |             |           | 7             |             | 7             |                 |          |                 |               | 7             |             |                 |                 | 7               |           |

| X86                          | >               | 7          | 7              | 7               | 7              | 7          | 7          | 7               | 7             | 7           | 7         | 7             | 7           | 7             | 7               | 7        | 7               | 7             | 7             | 7           | 7               | 7               |                 | 7         |

| ANALYSIS<br>SCOPE            | System          | System     | System         | System          | Process        | Process    | System     | System          | Process       | Process     | Process   | Process       | Process     | System        | System          | Process  | System          | System        | System        | Process     | System          | Process         | System          | System    |

| FINEST TAINT<br>GRANULARITY  | N/A             | Byte       | Bit            | Bit             | Bit            | Byte       | N/A        | N/A             | N/A           | Byte        | Byte      | Bit           | Byte        | Byte          | N/A             | Bit      | N/A             | N/A           | N/A           | N/A         | Byte            | Byte            | Byte            | Byte      |

| PLUGIN<br>SUPPORT            |                 |            | 2              | 2               | 2              | 2          |            |                 |               | 2           |           |               |             | 2             |                 | 2        |                 | 2             | 7             | 2           |                 |                 |                 | 7         |

| PURPOSE                      | Record/Replay   | Tainting   | General        | General         | General        | Tainting   | General    | Analysis Plugin | Symbolic Exec | Tainting    | Tainting  | Tainting      | Tainting    | Record/Replay | Analysis Plugin | General  | Analysis Plugin | Record/Replay | Symbolic Exec | General     | Tainting        | Tainting        | Tainting        | General   |

| TOOL                         | Aftersight [42] | Argos [77] | DECAF [62, 63] | DroidScope [88] | DynamoRIO [32] | DYTAN [43] | Ether [48] | HookFinder [91] | KLEE [36]     | libdft [69] | LIFT [78] | Memcheck [81] | Minemu [31] | PANDA [50]    | Panorama [90]   | Pin [70] | Renovo [67]     | ReVirt [51]   | S2E [40]      | Strata [80] | TaintBochs [41] | TaintCheck [75] | TaintDroid [53] | TEMU [16] |

Table 2.1: The scope and purpose of existing dynamic analysis tools.

14

analysis, it is necessary to automate the discovery of inputs that trigger interesting behaviors. Once interesting inputs are discovered, they can then later be replayed while the guest is executing under dynamic analysis. Work in the area of fuzzing has focused on discovering interesting input "seed" data (KLEE [36], AEG [26], COVERSET [79]) and fuzzing with symbolic execution (SAGE [59], Driller [83], TaintScope [84], Mayhem [38], Bitfuzz [35]). EmuFuzzer [71] fuzz tested various x86 emulators (QEMU [29], Valgrind [81], Pin [70], and Bochs [41]) for emulation correctness, showing that fuzz testing not only aids in performing dynamic analysis, but can be used to improve the analysis tools themselves.

The VDF fuzzing framework presented within this dissertation seeks to use record and replay (similar to that seen in tools like PANDA [50]), to test QEMU virtual devices. This provides a solution to the difficult problem of determining seed input that will trigger branches of interest within a complex program.

### **3. DECAF**

DECAF is built on top of QEMU [29], the whole-system emulator and dynamic translator. By extending QEMU, DECAF inherits a mature and feature-rich platform to use as a starting point when implementing its instrumentation and analysis functionality. Because all aspects of the guest environment (e.g. CPU, RAM, hardware devices) are emulated in software, DECAF has many opportunities to monitor the runtime behavior of the guest system.

QEMU's whole-system emulator functionality acts as a type-2 hypervisor for executing guest virtual machines (VMs). It makes use of dynamic binary translation techniques to emulate multiple target guest architectures, so the architecture of the guest environment can differ from that of the host machine. Virtual guest hardware devices, such as network interfaces and IDE/SCSI controllers, are implemented in software and pass data through to the devices physically present on the host system as needed.

QEMU decouples the specific details of the guest CPU from that of the host using its Tiny Code Generator (TCG). TCG translates the instructions of the guest environment into an intermediary representation (IR) of architecture-neutral set of RISC-like instructions. These instructions include common ALU operations (e.g. add, sub, xor), memory load/store, and control flow transfer. This IR is then dynamically translated into the native instructions of the host system and executed. This effectively decouples the CPU architecture and instruction set of the emulated guest environment from that of the host platform.

DECAF modifies QEMU's TCG to selectively insert instrumentation into the IR at the point of guest-to-IR translation. At the point of IR-to-host translation, the instrumentation becomes embedded within the host instruction stream without disturbing the semantic meaning of the guest's execution. This enables DECAF to support the analysis of a wide variety of different guest architectures while requiring only a minimal amount of architecture-specific code, and without requiring ad-hoc modifications to numerous subsystems. This process is detailed in Section 3.2.

#### 3.1 Key challenges

The following key challenges must be overcome when building a whole-system dynamic binary analysis platform:

**1. How to reconstruct a fresh OS-level semantic view from completely outside of the guest system?** As we run a virtual machine inside a whole-system binary analysis framework and perform various analysis tasks from outside, we must reconstruct the OS-level semantic view of the guest VM from outside, known as Virtual Machine Introspection (VMI). Several efforts (such as VMWatcher [66], Virtuoso [49], and VMST [56]) have been made to bridge this *semantic gap* and reconstruct the OS-level semantic view. However, the question of "when to reconstruct" has not been addressed. In a running system, the OS-level semantic views constantly change (e.g., a process starts or terminates, a code module is loaded or unloaded). For dynamic analysis, we must be

aware of these new events "just-in-time" at the moment they occur. The TEMU [82] analysis platform circumvented this problem by inserting a kernel module into the guest OS within the VM. This kernel module hooks several system events, retrieves OS-level information, and passes it to the hypervisor through a spare port. This circumvention clearly violates the external monitoring principle for VMI, and it can be easily subverted by the malicious code inside the VM.

DECAF proposes a new, novel solution to reconstructing a fresh OS-level semantic view by only monitoring hardware-level events. Such an approach has not, to our knowledge, been proposed before. It provides notification of OS-level events without requiring the expensive polling of guest kernel data structures or the violation of the external monitoring principle.

#### 2. How to provide an event-based programming paradigm that is both correct and

efficient? Most of the existing analysis platforms provide instrumentation interfaces only, through which a plugin can specify which instructions to instrument and what instrumentation code should be run. While this instrumentation approach is simple and flexible, it places a burden on the plugin developers to decide exactly how to instrument guest program execution. Such an approach is acceptable for user-level instrumentation, but it becomes difficult within a whole-system setting. Properly instrumenting whole-system execution requires the analyst to be familiar with the low-level system details of the guest system, such as exceptions, interrupts, page faults, context switches, etc.

Therefore, DECAF must provide an event-based interface, through which an analyst can register for events in various selected contexts (e.g., a process, the kernel space, or a kernel module). DECAF automatically determines what instrumentation code to selectively insert and where, and it ensures that the inserted instrumentation code is correct and efficient. TEMU provides a similar high-level interface, but achieves it in a naive way: it inserts instrumentation code uniformly in *all* translated code blocks and decides at execution time whether to deliver the events to the plugin. This guarantees the correctness of event processing, but incurs unnecessarily high runtime overhead. DECAF selectively inserts instrumentation into only the code blocks where it is needed, dramatically lowering overhead and improving performance.

**3.** How to implement precise, sound, and lossless tainting? Dynamic taint analysis (tainting) is a powerful dynamic binary analysis technique. Many taint system implementations exist [31, 43, 75, 78, 82]. Among these implementations, two important factors are often overlooked. First, most of these implementations are not *precise* enough (resulting in overtainting), and some of them are not even *sound* (resulting in undertainting). This means that these taint analysis systems would unnecessarily mark many memory locations as tainted and/or fail to taint certain memory locations and CPU registers that should be tainted. When dealing with security problems, an unsound implementation may miss real attacks, while an imprecise implementation may raise too many false alarms.

Second, we often need to track tainted data originating from multiple taint sources by applying multiple labels. Many taint analysis implementations do not distinguish among multiple taint labels. For the ones that do, they do not provide a lossless guarantee. Each tainted byte or word is associated with up to a small number of taint labels, due to space constraints on shadow memory. When a memory location or CPU register is tainted from more taint sources than those that can be kept in the shadow memory, the remaining are *lost*!

To achieve high precision, DECAF maintains taint information for every bit of registers and memory locations, and it applies precise tainting rules for most instructions at the QEMU TCG IR level. This thesis examines the information-flow patterns in integer operations experimentally, survey previous systems, and in several cases designs new propagation rules when no previous rule was sound and precise. The soundness and precision of these best rules are verified for each operation using two decision procedures (automatic theorem provers), and also using a new technique called *per-trace verification*. An analysis of these rules, using definitions based upon bit-level non-interference, is provided in Section 3.5.2.

To support any number of taint labels without the information loss seen in other systems, DECAF separates tracking of taint status from tracking taint labels. Taint status is tracked efficiently and inline during execution, while taint labels are tracked in an asynchronous manner via plugin-based logging. Taken together with its sound and precise information-flow rules, DECAF offers a novel, sound implementation of whole-system tainting without prohibitive amounts of runtime overhead.

**4.** How to provide strong support for cross-platform analysis? Ideally, the same analysis code (with minimum platform-specific code) works for different guest CPU

architectures (e.g., x86 and ARM) and different guest operating systems (e.g., Windows and Linux). This requires the analysis framework to hide guest architecture- and OS-specific details from the analysis plugins. Further, to make the analysis framework maintainable and easily extensible to new architectures and OSes, the platform-specific code within the framework must be minimized. Some instrumentation tools, like Pin [70], can run under both Linux and Windows, but, until now, no analysis tool provides support for both multiple architectures and multiple OSes. DECAF provides support for multiple platforms by implementing core instrumentation and analysis tasks at the TCG IR level, independent of the CPU architecture of the VM. DECAF's plugin API is engineered to hide many architecture and OS specific details.

#### **3.1.1 DECAF components**

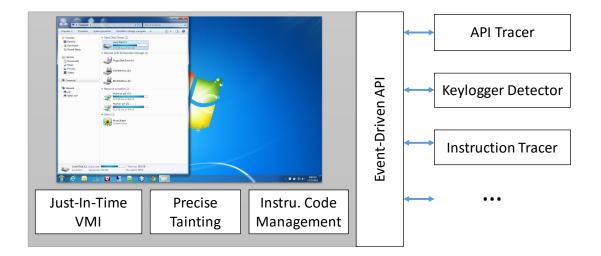

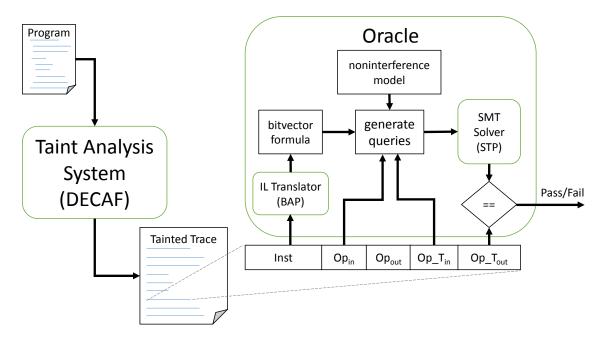

Figure 3.1 provides an overview of DECAF. Inside the virtual machine, programs of interest are run and various analyses are conducted externally via analysis plugins. DECAF has the following key components:

**Just-In-Time VMI.** DECAF's VMI component reconstructs a fresh, OS-level view of guest execution within the virtual machine, including each of the guest's processes, threads, code modules, and symbols, to support binary analysis. Further, to support multiple architectures and operating systems, DECAF follows a platform-neutral design principle. The workflow for extracting OS-level semantic information is common across multiple architectures and OSes. The only platform-specific handling lies in what guest

kernel data structures are examined and which fields to extract information from. Further details about the VMI implementation is provided in Section 3.3.

Precise, lossless dynamic taint analysis. DECAF ensures precise tainting by maintaining bit-level taint precision for CPU registers and memory, and inlining precise tainting rules within translated code blocks. Thus, the taint status of every CPU register and memory location is processed and updated synchronously during the code execution of the virtual machine. The propagation of taint labels is done by recording to a taint propagation log via a plugin. Later, this log can be analyzed to determine label propagation. This label analysis is done in an asynchronous manner for two reasons: 1) it is impractical and expensive to maintain an unlimited number of labels for each tainted bit in the shadow memory; and 2) for most taint analysis problems, it is not necessary to know which taint labels are associated with all tainted bits in real time. The majority of tainting analyses are only interested in when a key data sink (e.g., the x86 EIP register or a sensitive memory buffer) becomes tainted. Once taint reaches such a taint sink, the taint propagation log can be reviewed and the taint labels present in the sink retrieved. By implementing such a tainting logic mainly at QEMU's largely architecture-independent IR level, it becomes much simpler to extend tainting support to a new CPU architecture. Section 3.4 provides more details about DECAF's taint analysis implementation.

**Event-driven programming interface.** Compared to many existing analysis frameworks [70, 74] that provide only an instrumentation interface, DECAF provides an event-driven programming interface. This means that DECAF's design of "instrument in the translation phase and then analyze in the execution phase" is invisible to the analysis plugins. Plugins only need to register for specific events and implement the corresponding

Fig. 3.1.: The overview of DECAF.

event handling functions. The details of how the code is instrumented are handled by the framework, not by the plugins. Such details include how to generate the instrumentation code for inserting these event handlers into the translated code stream and how to maintain instrumentation code consistency when new event handlers are registered and old ones are removed.

**Dynamic instrumentation management.** To reduce runtime overhead to the guest environment, the instrumentation code is inserted into the translated IR code only where necessary. For example, when a DECAF plugin registers a function hook for a function's entry point, the instrumentation code for this hook is only placed once (at the function entry point). When the plugin unregisters this function hook, the instrumentation code will also be removed from the translated code accordingly. To ease the development of plugins, the management of dynamic code instrumentation is completely taken care of in the framework, and thus invisible to the plugins.

```

24

```

```

/* Define some globals for our plugin logic. */

static plugin_interface_t my_interface;

static DECAF_Handle handle_keystroke_cb;

static DECAF_Handle handle_read_taint_mem_cb;

static int taint_key_enabled = 0;

/* Define the callback triggered when tainted memory

is read. */

static void my_read_taint_mem_cb(DECAF_Callback_Params *param) {

char name[128];

tmodinfo_t tm;

/* Find the code module accessing tainted memory. */

if ( VMI_locate_module_c( DECAF_getPC(cpu_single_env),

DECAF_getPGD(cpu_single_env), name, &tm ) == 0 )

/* Virtual address and module of the access. */

DECAF_printf("INSN_0x\%08x, Module_'\%s'_Read_Key\n",

DECAF_getPC(cpu_single_env), tm.name);

}

/* Define the callback triggered when a keystroke is

entered into the guest via a QEMU monitor command. */

static void my_sendkey_cb(DECAF_Callback_Params * params) {

*params->ks.taint_mark = taint_key_enabled;

taint_key_enabled = 0;

DECAF_printf("taint_key_%d_\n", params->ks.keycode);

}

/* Define the function called when the plugin-specific

"taint_sendkey" QEMU monitor command is used. */

static void do_taint_sendkey(Monitor *mon, const QDict *qdict) {

if (qdict_haskey(qdict, "key")) {

/* Enable tainting for the next keystroke */

taint_key_enabled = 1;

/* Send the tainted keystroke into the guest */

do_send_key(qdict_get_str(qdict, "key"));

}

}

/* Define the "taint_sendkey" QEMU monitor command. */

static mon_cmd_t my_term_cmds[] = {

{

= "taint_sendkey",

. name

.args_type = "key:s",

.mhandler.cmd = do_taint_sendkey,

.params = "taint_sendkey_key",

. help = "Send_a_tainted_keypress_to_the_guest"

\{NULL, NULL, \},

};

/* Define a cleanup function for plugin unload. */

static void my_cleanup(void) { /* Perform cleanup here. */ }

/* This is executed upon loading this plugin. */

plugin_interface_t *init_plugin(void) {

/* Register plugin-specific QEMU monitor commands. */

my_interface.mon_cmds = my_term_cmds;

/* Register cleanup function called at plugin unload. */

my_interface.plugin_cleanup = my_cleanup;

/* Register for DECAF callback events. */

handle_read_taint_mem_cb = DECAF_register_callback(

DECAF_READ_TAINTMEM_CB, my_read_taint_mem_cb, NULL);

handle_keystroke_cb = DECAF_register_callback (

DECAF_KEYSTROKE_CB, my_sendkey_cb, NULL);

/* Done! Return this new plugin interface to DECAF. */

return &my_interface;

}

```

Fig. 3.2.: A sample plugin for tracking tainted keystrokes.

#### **3.1.2 Example DECAF Plugin**

Figure 3.2 presents the source code for an example DECAF plugin that detects keylogger malware within the guest system. This plugin tracks the propagation of tainted keystrokes throughout the entire guest environment, and it is both guest architecture and OS independent. The same plugin code works for x86 and ARM, Windows and Linux. Whenever possible, DECAF provides generic functions to abstract away any architecture-dependent details of the guest. For example, DECAF\_getPC will return the program counter (e.g., EIP in x86 and R15 in ARM), and DECAF\_getPGD will return the page table directory (e.g., CR3 in x86 and CP15 in ARM).

DECAF plugins work by registering callback functions that are executed when events of interest occur within the guest. The sample plugin defines two functions, my\_read\_taint\_mem\_cb and my\_sendkey\_cb, that ware registered as callback functions. my\_read\_taint\_mem\_cb is called whenever tainted guest memory is read (the DECAF\_READ\_TAINTMEM\_CB event). my\_sendkey\_cb is called whenever a tainted keystroke is entered into the system (the DECAF\_KEYSTROKE\_CB event).

Because it is often necessary for an analyst to interact with a plugin during guest execution, DECAF leverages the QEMU command monitor. The monitor is a shell that accepts commands for controlling and querying the runtime behavior of QEMU, such as starting/stopping guest execution, saving the state of the VM, and profiling QEMU's resource usage. The example plugin code specifies a plugin-specific monitor command, taint\_sendkey, in the my\_term\_cmds[] array. When this command is entered into the QEMU monitor, the plugin's do\_taint\_sendkey function is called and a tainted keypress is entered into the guest VM. The taint\_sendkey command is only available while the plugin is loaded. Upon unloading the plugin, any plugin-specific commands are removed from the monitor.

Every plugin must have an init\_plugin function. This function is called to initialize the plugin and return a pointer to a plugin\_interface\_t structure, which specifies any plugin-specific monitor commands and a cleanup function (my\_cleanup in the sample plugin) to be called when the plugin is unloaded. The init\_plugin function typically registers callback functions for any guest events of interest, but registering and unregistering callbacks can be performed at any point after the plugin has been loaded.

When the analyst loads this sample plugin and then enters the taint\_sendkey command into the monitor, the registered callback my\_send\_keystroke is called and the corresponding keystroke is tainted. Thereafter, the tainted keystroke will propagate from the keyboard device, through the OS kernel, and to the destination user-level program. Since DECAF performs whole-system dynamic taint analysis, the analyst is able to observe this entire taint propagation flow. Whenever an instruction reads a tainted memory location, the DECAF calls the registered my\_read\_tainted\_mem callback, which checks the code module in which this instruction is located. Any relevant information about this taint event is then logged for offline analysis.

#### **3.2** Selective Code Instrumentation

To meet the requirements of efficiency and cross-platform for code instrumentation, DECAF selectively inserts instrumentation code at QEMU's intermediate representation (IR) level.

**Dynamic binary translation in QEMU.** To support multiple architectures, QEMU makes use of a compiler backend, called Tiny Code Generator (TCG), as its dynamic binary translation engine. QEMU translates each basic block of guest instructions into an architecture-independent TCG IR instructions within a TCG translation block (TB). The TCG compiler then translates each TB into a piece of native code to be executed on the host. Figure 3.3(a) provides an example of how two x86 instructions are translated into these TCG instructions.

TCG instructions include common ALU operations (e.g. add, sub, xor), memory load/store, and control flow transfer. The parameters for each TCG instruction can be temporary variables (registers that exist only within the scope of the current TB), global variables, and constants. For more complex, guest-specific instructions (e.g. floating point operations), a call TCG instruction exists for making calls to high-level language helper functions that implement the complex functionality. In this manner, TCG cleanly decouples specific details of the guest's architecture and instruction set from that of the host.

**Placement of code execution events.** DECAF's code instrumentation integrates coherently into the TCG-based dynamic binary translation process. Events like "block begin/end" (for reaching the beginning/end of a TB) and "instruction begin/end" (for

reaching the IR that begin/end a guest instruction) are used for tracing guest execution. When callbacks for these events are registered by a plugin, DECAF inserts the proper helper function calls into the necessary TBs by pausing the guest's execution, flushing the necessary TBs, retranslating those TBs to include calls to the helper functions (via an inserted call IR), and then resuming the guest's execution. Because callbacks are triggered inline with the guest's execution, they are guaranteed to be synchronized to the occurance of events of interest.

Figure 3.3(b) shows the insertation of the two helper functions DECAF\_invoke \_insn\_begin\_callback and DECAF\_invoke\_insn\_end\_callback at the beginning and end of each guest instruction, respectively. For many analyses, the analyst is only interested in the execution of a small subset of the guest system, such as the instructions belonging to a single kernel module or user-level process. Plugins can specify ranges of memory addresses, or even a single address, of interest when registering for callbacks. Callback helper functions are only placed into the necessary TBs, and only at the proper locations within each TB, to capture these events as they occur. This greatly reduces the runtime overhead of DECAF.

An important design decision of DECAF is its callback dispatch mechanism. For each kind of event (e.g., "block begin"), only a single helper function (e.g., DECAF\_invoke \_block\_begin\_callback) is inserted at each desired program location. Within the helper function, DECAF iterates through all registered callbacks for that event and decides which callbacks to trigger. There are two important reasons for this: avoiding multiple callbacks at the same location and efficiently removing stale instrumentation code.

// Start of translation block // Original instruction: orl %ebx, %eax mov\_i3Ž tmp11. ebx  $mov_i 32$ tmp12, eax or\_i32 tmp13, tmp12, tmp11 // Original instruction: addl \$0x01, %eax movi\_i32 tmp14. \$0x01 add\_i32 tmp15, tmp14, tmp13  $mov_i 32$ eax, tmp15 // End of translation block goto\_tb \$0x0

(a)

// Start of translation block // Insert DECAF\_BLOCK\_BEGIN callback movi\_i32 tmp21, \$<CURRENT\_ADDRESS> movi\_i32 tmp22, \$DECAF\_invoke\_block\_begin\_callback tmp22, \$0x0, \$0, env, tmp21